Driving clocks with FPGAs

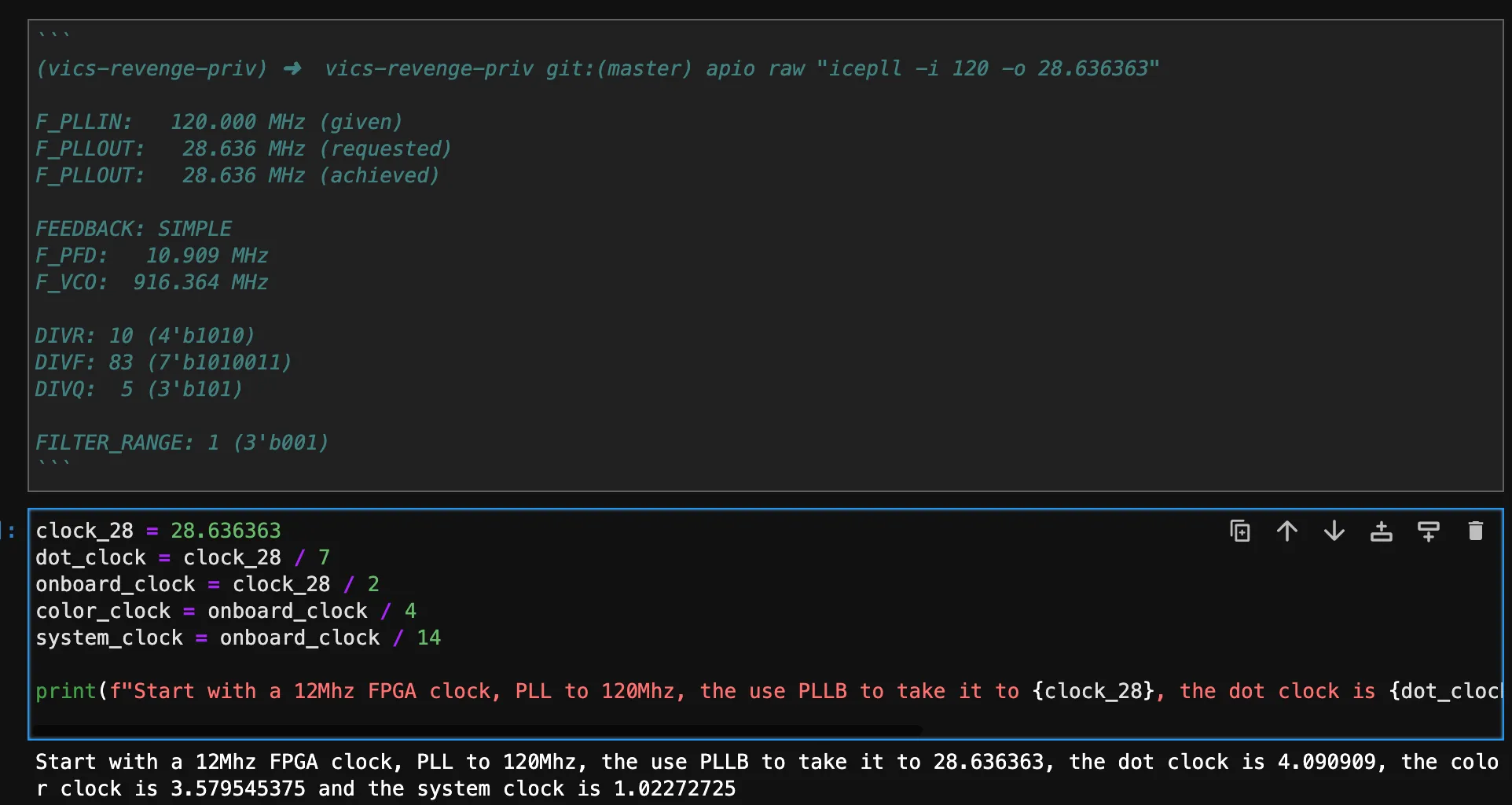

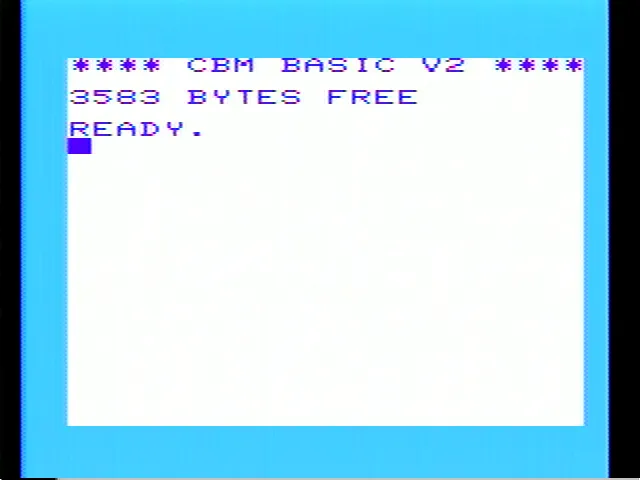

Here are some clues if you were wondering how to create the 3 clocks you need to drive an NTSC VIC-20 from a 12Mhz onboard clock on an FPGA with 2 PLLs. I can’t think of a better way to contribute to this machine’s legacy than to make it possible for others to do what I’m doing. The goal is to create an OPEN replacement for the only chip on a VIC-20 that doesn’t have a modern replacement. (yes, this will be a LONG post on the website)